- 您现在的位置:买卖IC网 > Sheet目录2001 > ISL12032IVZ (Intersil)IC RTC LP BATT BACK SRAM 14TSSOP

19

FN6618.3

May 5, 2011

ACFP = 11b (10 total AC cycles)

So the resulting crystal cycle count must be within:

±(10 AC cycles x 2 crystal cycles/AC cycle) or

± 20 total crystal cycles (error budget) as shown in Table 23.

Fine Trim Compensation Register (FTR)

This register (Table 24) provides control of the crystal

oscillator clock compensation and the AC clock input

minimum level detect.

AC MINIMUM (ACMIN)

This bit determines the minimum peak-to-peak voltage level

for the AC clock input as a percentage of the existing VDD

supply. ACMIN = 0 sets the minimum level to 5% x VDD.

ACMIN = 1 sets the minimum level to 10% x VDD.

DIGITAL TRIM REGISTER (XDTR<3:0>)

The digital trim register bits control the amount of trim used

to adjust for the crystal clock error. This trim is accomplished

by adding or subtracting the 32kHz clock in the clock counter

chain to adjust the RTC clock. Calibration can be done by

monitoring the FOUT pin with a frequency counter with the

frequency output set to 1.0Hz, with no AC input.

DST Control Registers (DSTCR)

8 bytes of control registers have been assigned for the

Daylight Savings Time (DST) functions. DST beginning (set

Forward) time is controlled by the registers DstMoFd,

DstDwFd, DstDtFd, and DstHrFd. DST ending time (set

Backward or Reverse) is controlled by DstMoRv, DstDwRv,

DstDtRv and DstHrRv.

DSTCR.

DST FORWARD REGISTERS (15H TO 18H)

DSTE is the DST Enabling Bit located in bit 7 of register 15h

(DstMoFdxx). Set DSTE = 1 will enable the DSTE function.

Upon powering up for the first time (including battery), the

DSTE bit defaults to “0”.

DST forward is controlled by the following DST Registers:

DstMoFd sets the Month that DST starts. The default value

for the DST begin month is April (04h)

.

DstDwFd sets the Day of the Week that DST starts.

DstDwFdE sets the priority of the Day of the Week over the

Date. For DstDwFdE = 1, Day of the week is the priority.

Note that Day of the week counts from 0 to 6, like the RTC

registers. The default for the DST Forward Day of the Week

is Sunday (00h).

DstDtfd controls which Date DST begins. The default value

for DST forward date is on the first date of the month (01h).

DstDtFd is only effective if DstDwFdE = 0.

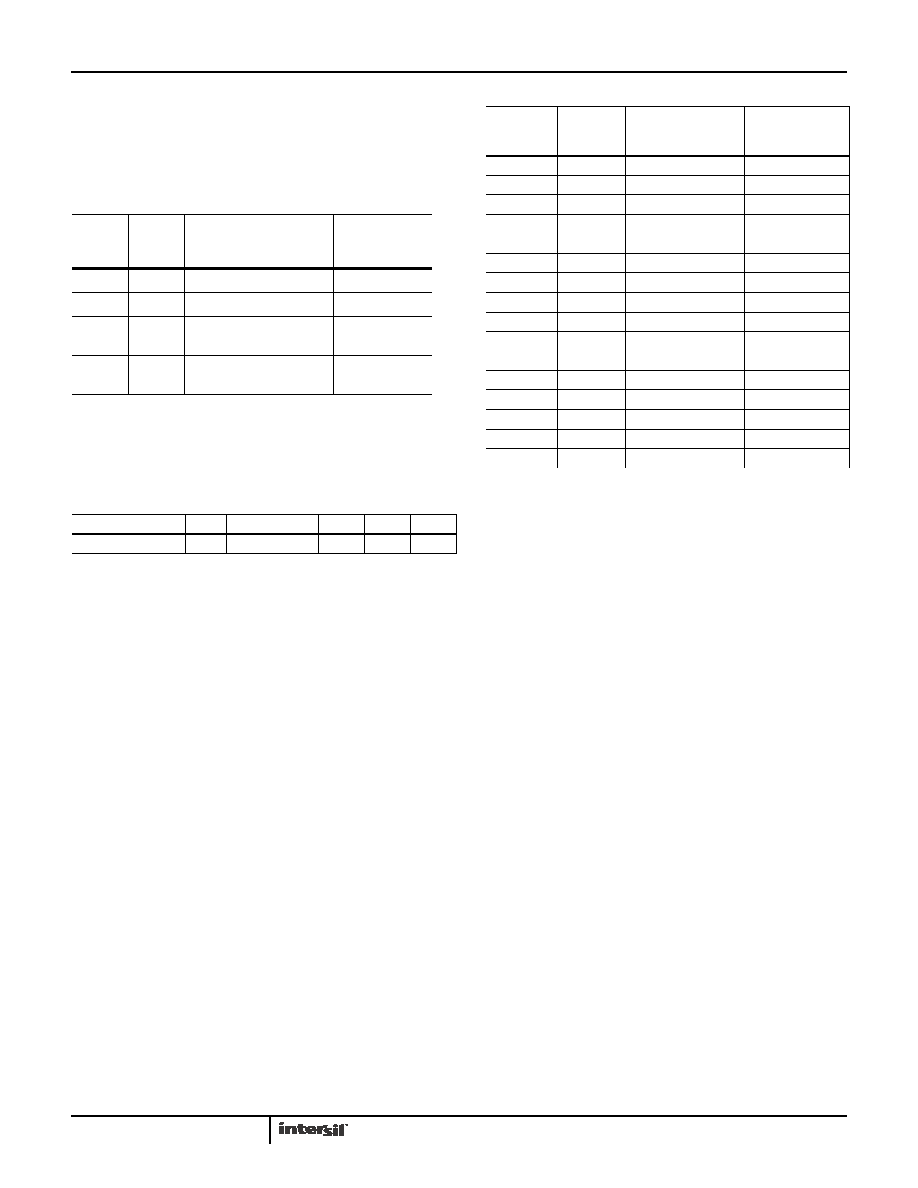

TABLE 23. AC/CRYSTAL FREQUENCY FAILURE CRITERION

ACFC1

ACFC0

CRITERION

TOTAL XTAL

CYCLE ERROR

BUDGET

0

1 crystal cycle per AC cycle

ACFP x 1

0

1

2 crystal cycle per AC cycle

ACFP x 2

1

0

1 crystal cycle in all AC

cycles

1

2 crystal cycles in all AC

cycles

2

TABLE 24. FINE TRIM COMPENSATION REGISTER

ADDR

7

6

5

4

3210

14h

X

ACMIN XDTR3 XDTR2 XDTR1 XDTR0

TABLE 25. XDTR FREQUENCY COMPENSATION

XDTR3

XDTR2

XDTR1

XDTR0

FREQUENCY

COMPENSATION

(ppm)

00

0

00

0

1

10

00

1

0

20

00

1

30

01

0

40

01

0

1

50

01

1

0

60

01

1

0

10

0

10

0

1

-10

10

1

0

-20

10

1

-30

11

0

-40

11

0

1

-50

11

1

0

-60

11

1

0

ISL12032

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL12057IUZ

IC RTC/CALENDAR I2C 8-MSOP

ISL12058IUZ

IC RTC/CALENDAR I2C-BUS 8-MSOP

ISL12059IBZ

IC RTC/CALENDAR I2C-BUS 8-SOIC

ISL12082IUZ

IC RTC I2C LO-POWER 10-MSOP

ISL1208IU8-TK

IC RTC/CALENDAR I2C 8-MSOP

ISL1209IU10-TK

IC RTC/CALENDAR I2C 10-MSOP

ISL1218IUZ

IC RTC LP BATT BACKED SRAM 8MSOP

ISL1219IUZ-T

IC RTC LP BATT BACK SRAM 10MSOP

相关代理商/技术参数

ISL12032IVZ-T

功能描述:实时时钟 REAL TIME CLK W/ EEPROM 14LD RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12057

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Cost and Low Power I2C RTC Real Time Clock/Calendar

ISL12057IBZ

功能描述:实时时钟 REAL TIME CLK W/ ALARM DS1337 COMP RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12057IBZ-T

功能描述:实时时钟 REAL TIME CLK W/ ALARM DS1337 COMP RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12057IRUZ-T

功能描述:实时时钟 REAL TIME CLK W/ ALARM DS1337 COMP RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12057IUZ

功能描述:实时时钟 REAL TIME CLK W/ ALARM DS1337 COMP RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12057IUZ-T

功能描述:实时时钟 REAL TIME CLK W/ ALARM DS1337 COMP RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12058

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Cost and Low Power I2C-Bus? Real Time Clock/Calendar